巴黎世家 丝袜

亚洲美女色图-欧美裸体色图-亚洲色图 5nm芯片集体“翻车”,先进制程的难受

作家 | 吴优亚洲美女色图-欧美裸体色图-亚洲色图

出品 | 雷锋网产业组

先进制程的性价比下落了吗?

1

5nm芯片集体“翻车”,从7nm到5nm的难受

最早商用的5nm芯片是客岁10月份iPhone12系列手机搭载的A14仿生芯片,这款芯片晶体管达到118亿个,比A13多出近40%,且6核CPU和4核GPU使其CPU性能普及40%,图形性能普及30%,功耗诽谤30%。

紧接着华为发布麒麟9000,集成153亿个晶体管,8核CPU、24核GPU和NPU AI处理器,官方称其CPU性能普及25% ,GPU普及50%。

到了十二月份,高通和三星又接踵发布了由三星代工的骁龙888和Exynos 1080,一样宣称性能有较大普及,功耗下落。

开始被爆出疑似“翻车”的是A14。

据外媒9to5Mac报谈,部分iPhone 12用户在使用手机时碰到了高耗电问题,待机今夜电量下落20%至40%,不管是在白日照旧晚上,不管有莫得开启更多的后台法子,效能依旧如斯。

最广为用户诟病的还属骁龙888。

在首批使用者的测试中,不少数码评测博主皆指出首发骁龙888的小米11性能普及有限,功耗奏凯飞腾。有东谈主将此归结于骁龙888的代工场三星的5nm工艺制程的不教训,由此以来三星我方的两款5nm芯片也面对“翻车”风险。

淌若按照摩尔定律,芯片的晶体管数量每隔18个月翻一番,性能也将普及一倍,但晶体管的微缩越来越难,如今在从7nm到5nm的鼓动中,手机芯片的推崇似乎并不尽东谈认识,不仅在性能普及方面受限,功耗也“翻车”,面对先进制程性价比上的难受。

为何5nm芯片频频翻车?当芯片工艺制程越先进时,性能与功耗究竟若何变化?

2

假想时性能优先,制造时工艺不教训

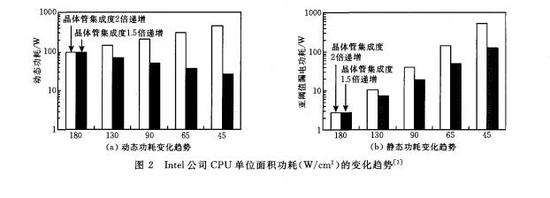

集成电路的功耗不错分为动态功耗和静态功耗亚洲美女色图-欧美裸体色图-亚洲色图。

动态功耗阳春白雪,指的是电路情状变化时产生的功耗,狡计递次与时常电路肖似,依据物理公式P=UI,动态功耗受到电压和电流的影响。

静态功耗即每个MOS管暴露电流产生的功耗,尽管每个MOS管产生的走电流很小,但由于一颗芯片频频集成上亿以至上百亿的晶体管,从而导致芯片举座的静态功耗较大。

在芯片工艺制程发展历程中,当工艺制程还不太先进时,动态功耗占比大,业界通过覆没领先的5V固定电压的假想格局,取舍等比降压降速功耗的增长速率。

不外,电压减小一样意味着晶体管的开关会变慢,部分愈加审视性能的厂商,即就是取舍更先进的工艺也依然保合手5V供电电压,最终导致功耗增大。

跟着工艺节点的逾越,静态功耗的伏击性冉冉流露。从英特尔和IBM的芯片工艺发展中不错看出,在工艺制程从180nm到45nm的演进历程中,晶体管集成度增速不同,动态功耗或增多或减少,但静态功耗一直呈飞腾趋势,丝袜脚 45nm时,静态功耗确切与动态功耗合手平。

智慧树在线教育平台

尽管一些假想厂商答应在诽谤功耗上作念出糟跶也要普及性能,但也不得不面对高功耗带来的负面影响。

关于用户而言,诞生发烧严重以及耗电严重是高功耗带来的奏凯影响,淌若芯片散热不好,严重时会导致芯片额外以至失效。

因此,行业内依然将低功耗假想视为芯片行业需要惩办的问题之一,若何均衡先进节点下芯片的性能、功耗与面积(PPA),亦然芯片假想与制造的挑战。

从表面上而言,芯片制程越先进,更低的供电电压产生更低的动态功耗,跟着工艺尺寸进一步减小,已下落到0.13V的芯片电压难以进一步下落,以至于近几年工艺尺寸进一步减小时,动态功耗基本无法进一步下落。

在静态功耗方面,场效应管的沟谈寄生电阻随节点逾越而变小,在电流不变的情况下,单个场效应管的功率也变小。但另一方面,单元面积内晶体管数量倍速增长又普及静态功耗,因此最终单元面积内的静态功耗可能保合手不变。

厂商为追求更低的成本,用更小面积的芯片承载更多的晶体管,看似是达成了制程越先进,芯片性能越好,功耗越低。但骨子情况频频复杂得多,为普及芯片举座性能,有东谈主增多中枢,有东谈主假想更复杂的电路,随之而来的是更多的旅途刺激功耗增长,又需要新的递次来均衡功耗。

对芯片行业影响首要的FinFET就是均衡芯片性能与功耗的递次之一,通过肖似于鱼鳍式的架构限度电路的聚合和断开,改善电路限度并减少走电流,晶体管的沟谈也随之大幅度镌汰,静态功耗随之诽谤。

不外,从7nm演进到5nm则更为复杂。

Moortec首席技艺官Oliver King曾接收外媒体采访时称:“当咱们升级到16nm或14nm时,处理器速率有了很大的提高,何况走电流也下落得相比快,以至于咱们在使用处理器时八成用有限的电量作念更多的事情。不外当从7nm到5nm的历程中,走电情况又变得严重,确切与28nm水平疏导,目下咱们不得不去均衡他们。”

Cadence的数字和签准组高等家具料理总监Kam Kittrell曾经暗意,“许多东谈主皆莫得弄清八成耗尽如斯多电能的东西,他们需要提前取得责任负载的信息才智优化动态功耗。弥远以来,咱们一直专注于静态功耗,以至于一朝切换到FinFET节点时,动态功耗就成为大问题。另外多中枢的出现也有可能使系统过载,因此必须有更智能的惩办有计议。”

这是5nm芯片假想、制造公司共同面对的问题,因此也就八成略微清爽为何现存的几款5nm芯片集体“翻车”。不教训的假想与制造皆会影响性能与功耗的最大化折中,虽然也不摒除芯片假想厂商为追求性能更好的芯片,而不肯花自便气诽谤功耗的情况。

难受的是,越顶尖的工艺,需要的资金过问就越大,事实上追求诸如7nm、5nm等先进工艺的边界并未几,淌若先进的工艺无法在功耗与性能上有极大的改善,那么追求愈加先进的制程似乎不再有底本的真谛。

3

走向3nm,确凿准备好了吗?

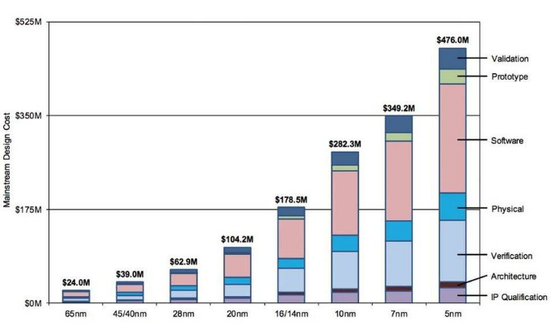

凭据商场参议机构International Business Strategies (IBS)给出的数据夸耀,65nm 工艺时的假想成本只需要0.24亿好意思元,到了28nm工艺时需要0.629亿好意思元,7nm和5nm成本急速增长,5nm假想成本达到4.76亿好意思元。

同期,凭据乔治敦大学沃尔什社交学院安全与新兴技艺中心(CSET)的两位作家编写的一份题为《AI Chips: What They Are and Why They Matter》的讲述,作家借助模子预估得出台积电每片5nm晶圆的收费可能约为17,000好意思元,是7nm的近两倍。

在估算的模子中,作家估算出每颗5nm芯片需要238好意思元的制变成本,108好意思元的假想成本以及80好意思元的封装和测试成本。这使得芯片假想公司将为每颗5nm芯片支付高到426好意思元(约2939元)的总成本金额。

这意味着,不管是芯片假想厂商照旧芯片制造厂商,受命摩尔定律发展到5nm及以下的先进制程,除了需要冲突技艺上的瓶颈,还需要有宽广的成本动作营救,熬过研发周期和测试周期,为商场提供功耗和性能均有改善的芯片最终进入答复期。

因此,并不是业界通盘东谈主皆对5nm芯片的鼓动合手积极乐不雅的派头。芯片IP供应商Kandou的首席试验官Amin Shokrollahi曾在接收外媒采访时暗意:“对咱们而言,从7nm到5nm 是令东谈主讨厌的,电路不会按比例缩放,何况需要许多用度,咱们莫得看到这其中的上风。关联词客户但愿咱们这么作念,是以咱们不得不这么作念。”

还有各人第二大芯片代工场Global Foundries出于经济磋商,于2018年秘书扬弃7nm 技俩,将资源归来12nm/14nm 上。就连实力强盛的英特尔也在10nm、7nm的研发历程中屡次受阻。

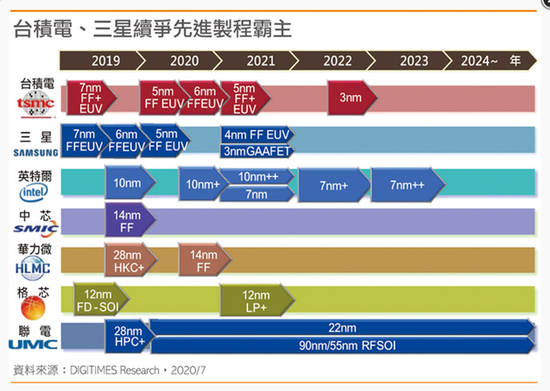

不外,这依然无法进攻各家手机芯片假想厂商在先进制程上的竞争,更无法进攻三星和台积电之间的制程霸主争夺。

此前雷锋网报谈过,在先进制程的芯片制造方面,三星视台积电为最大的竞争敌手,三星在同台积电的竞争中,先进制程的鼓动断断续续,仍是为了后发制东谈主奏凯从7nm跳到7nm LPP EUV,二者同期在2020年竣事5nm FF EUV 的量产,如今又皆斥巨资过问3nm的研发与量产中。

上周五,台积电CEO魏哲家在投资东谈主会议上秘书,台积电2021年景本的开销将高到250亿至280亿好意思元,其中80%会使用在包括3nm、5nm及7nm的先进制程上,10%用在高端封装及光罩作用,另外10%用在特殊制程上。

凭据台积电3nm制程的进程,瞻望将在2021年试产,在2022年下半年进入量产,匡助英特尔代工3nm处理器芯片。

与此同期,三星曾经对外称其3nm GAA的成本可能会超越5亿好意思元,预期在2022年大限制坐蓐取舍比FinFET更为先进的GAAFET 3nm制程芯片。

归来到5nm迁移处理器的骨子情况,不管是出自哪家厂商的假想与坐蓐亚洲美女色图-欧美裸体色图-亚洲色图,均面对性能和功耗方面的问题,5nm芯片似乎还未教训,3nm量产就要本年启动试产。越来越趋于摩尔定律极限的3nm,确凿准备好了吗?